RTL工程目錄介紹

本文為您介紹RTL(Register Transfer Level)開發(fā)平臺所使用的工程模式及目錄介紹,并提供RTL示例框架幫助您理解并使用。

工程模式

Vivado設(shè)計套件是由FPGA廠商發(fā)布的集成設(shè)計環(huán)境,具有NoProject和Project兩種工程模式,具體說明如下所示:

NoProject模式

該模式需要將多個DCP文件整合成一個DCP文件,然后運行布局布線后,最終生成

bit文件。F3實例的RTL開發(fā)平臺采用的是NoProject模式。Project模式

該模式需要創(chuàng)建一個整體的工程,例如:創(chuàng)建一個

XXX_prj.xpr工程,然后導(dǎo)入所需要的RTL代碼和約束文件,最終生成bit文件。

工程主目錄介紹

工程目錄包含主目錄和source目錄。source目錄下是PR(Pull Request)區(qū)域的相關(guān)工程文件,主目錄下是運行工程的腳本文件,主目錄的具體說明如下:

腳本名稱 | 描述 |

compiling.sh | 運行整體工程的腳本,最終生成xclbin加載文件。 |

create_design.tcl | 在Vivado Tcl Console中執(zhí)行的腳本,該腳本以 |

mem_design.tcl | 在Vivado Tcl Console中執(zhí)行的腳本,該腳本重新實例化了DDR IP文件,需要和 |

run_synth.tcl | 需要和 |

run.tcl | 整體運行的腳本,被 |

generate_dcp.tcl | 該腳本在整合成一個完整的dcp文件后,將生成最終的dcp文件和bit文件,您可以根據(jù)自己的需要進(jìn)行策略修改。 |

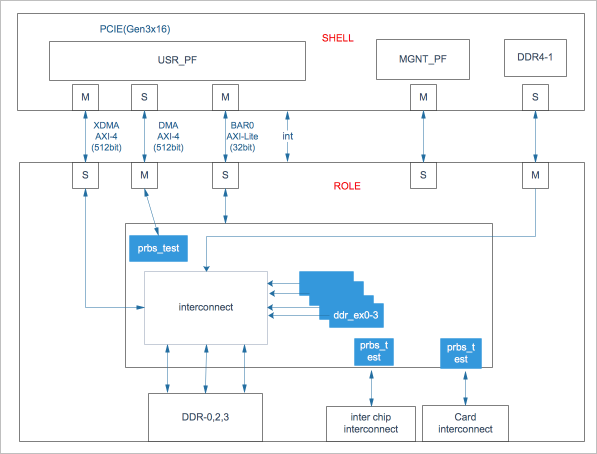

RTL示例框架

在RTL模式下,我們提供了一個基于如下框架的參考示例。

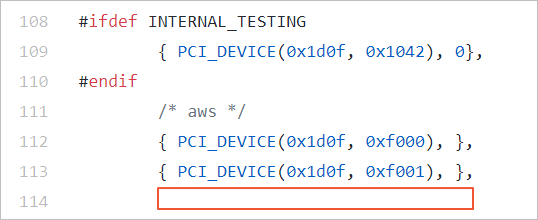

您可以在示例代碼的如下位置,添加

{ PCI_DEVICE(0x1ded, 0x1004), },完成device id的修改,即可直接使用其中的工具進(jìn)行測試。AR65444軟件和工具的相關(guān)說明請前往XIlinx官網(wǎng)查看。

您可以在Vivado界面的Tcl Console中執(zhí)行

create_design.tcl,建立用戶工程,測試綜合過程。整體工程完成之后,您可以通過Vivado打開dcp文件,然后查看資源、時序和布線結(jié)果等信息。